# FTCD4543E2PXM

# 4x100G-LR QSFP-DD Optical Transceiver Module

FTCD4543E2PxM QSFP-DD transceiver modules are designed for use in 400 Gigabit Ethernet links on up to 10km of single mode fiber. They are compliant with the QSFP-DD MSA, QSFP28 MSA<sup>3</sup>, IEEE 802.3cu<sup>2</sup> and portions of IEEE P802.3bm<sup>6</sup>. Digital diagnostic functions are available via the I2C interface, as specified by the QSFP28 MSA and Finisar Application Note AN-20xx<sup>5</sup>. The transceiver is RoHS-6 compliant per Directive 2011/65/EU<sup>4</sup> and Finisar Application Note AN-2038<sup>5</sup>.

# **FEATURES**

- Hot-pluggable QSFP-DD type 2 form factor

- Supports 425Gb/s aggregate bit rate

- 10 km over parallel SMF

- Power dissipation <10W (limited temp) or < 12W (c-temp)

- RoHS-6 compliant

- Case temperature range of 20°C to +60°C (limited temp) or 0°C to +70°C (c-temp)

- Single 3.3V power supply

- 4x100Gb/s PAM4 serial lanes

- 8x50G PAM4 retimed electrical interface

- Parallel MPO receptacle

- I2C management interface10B

# **APPLICATIONS**

- 4x100G-LR applications with FEC

- 100GbE breakout applications

### **Product Selection**

# FTCD4543E2PxM

E: Ethernet protocol

P: Pull-tab type release

C or L: Commercial or Limited temperature range

M: MPO receptacle

### I. Pin Descriptions

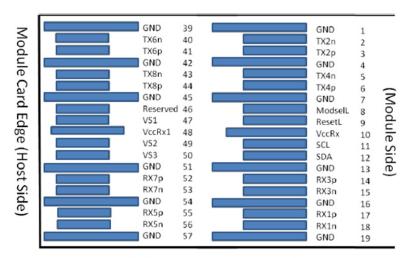

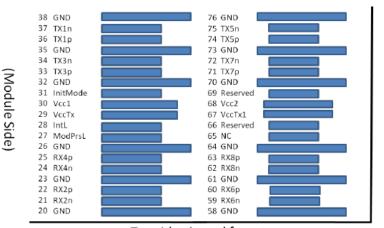

# Bottom side viewed from bottom

Module Card Edge (Host Side)

Top side viewed from top

Figure 1 – QSFP-DD -compliant 76-pin connector (per QSFP-DD MSA)

# FTCD4543E2PXM

| Pin | Logic      | Symbol   | Name/Description                    | Plug Sequence4 | Notes |

|-----|------------|----------|-------------------------------------|----------------|-------|

| 1   |            | GND      | Ground                              | 1B             | 1     |

| 2   | CML-I      | Tx2n     | Transmitter Inverted Data Input     | 3B             |       |

| 3   | CML-I      | Tx2p     | Transmitter Non-Inverted Data Input | 3B             |       |

| 4   |            | GND      | Ground                              | 1B             | 1     |

| 5   | CML-I      | Tx4n     | Transmitter Inverted Data Input     | 3B             |       |

| 6   | CML-I      | Тх4р     | Transmitter Non-Inverted Data Input | 3B             |       |

| 7   |            | GND      | Ground                              | 1B             | 1     |

| 8   | LVTTL-I    | ModSelL  | Module Select                       | 3B             |       |

| 9   | LVTTL-I    | ResetL   | Module Reset                        | 3B             |       |

| 10  |            | Vcc Rx   | +3.3 V Power supply receiver        | 2B             | 2     |

| 11  | LVCMOS-I/O | SCL      | 2-wire serial interface clock       | 3B             |       |

| 12  | LVCMOS-I/O | SDA      | 2-wire serial interface data        | 3B             |       |

| 13  |            | GND      | Ground                              | 1B             | 1     |

| 14  | CML-O      | Rx3p     | Receiver Non-Inverted Data Output   | 3B             |       |

| 15  | CML-O      | Rx3n     | Receiver Inverted Data Output       | 3B             |       |

| 16  |            | GND      | Ground                              | 1B             | 1     |

| 17  | CML-O      | Rx1p     | Receiver Non-Inverted Data Output   | 3B             |       |

| 18  | CML-O      | Rx1n     | Receiver Inverted Data Output       | 3B             |       |

| 19  |            | GND      | Ground                              | 1B             | 1     |

| 20  |            | GND      | Ground                              | 1B             | 1     |

| 21  | CML-O      | Rx2n     | Receiver Inverted Data Output       | 3B             |       |

| 22  | CML-O      | Rx2p     | Receiver Non-Inverted Data Output   | 3B             |       |

| 23  |            | GND      | Ground                              | 1B             | 1     |

| 24  | CML-O      | Rx4n     | Receiver Inverted Data Output       | 3B             |       |

| 25  | CML-O      | Rx4p     | Receiver Non-Inverted Data Output   | 3B             |       |

| 26  |            | GND      | Ground                              | 1B             | 1     |

| 27  | LVTTL-O    | ModPrsL  | Module Present                      | 3B             |       |

| 28  | LVTTL-O    | IntL     | Interrupt                           | 3B             |       |

| 29  |            | Vcc Tx   | +3.3 V Power supply transmitter     | 2B             | 2     |

| 30  |            | Vcc1     | +3.3 V Power Supply                 | 2B             | 2     |

| 31  | LVTTL-I    | InitMode | Low Power Mode                      | 3B             |       |

| 32  |            | GND      | Ground                              | 1B             | 1     |

| 33  | CML-I      | Тх3р     | Transmitter Non-Inverted Data Input | 3B             |       |

| 34  | CML-I      | Tx3n     | Transmitter Inverted Data Input     | 3B             |       |

| 35  |            | GND      | Ground                              | 1B             | 1     |

| 36  | CML-I      | Tx1p     | Transmitter Non-Inverted Data Input | 3B             |       |

| 37  | CML-I      | Tx1n     | Transmitter Inverted Data Input     | 3B             |       |

| 38  |            | GND      | Ground                              | 1B             | 1     |

| 39  |            | GND      | Ground                              | 1A             | 1     |

| 40  | CML-I      | Tx6n     | Transmitter Inverted Data Input     | 3A             |       |

| 41  | CML-I      | Тх6р     | Transmitter Non-Inverted Data Input | 3A             |       |

| 42  |            | GND      | Ground                              | 1A             | 1     |

### FTCD4543E2PXM

| 43 | CML-I | Tx8n     | Transmitter Inverted Data Input     | 3A |   |

|----|-------|----------|-------------------------------------|----|---|

| 44 | CML-I | Tx8p     | Transmitter Non-Inverted Data Input | 3A |   |

| 45 |       | GND      | Ground                              | 1A | 1 |

| 46 |       | Reserved | For future use                      | ЗА | 3 |

| 47 |       | VS1      | Module Vendor Specific 1            | 3A | 3 |

| 48 |       | VccRx1   | 3.3 V Power Supply                  | 2A | 2 |

| 49 |       | VS2      | Module Vendor Specific 2            | 3A | 3 |

| 50 |       | VS3      | Module Vendor Specific 3            | 3A | 3 |

| 51 |       | GND      | Ground                              | 1A | 1 |

| 52 | CML-O | Rx7p     | Receiver Non-Inverted Data Input    | 3A |   |

| 53 | CML-O | Rx7n     | Receiver Inverted Data Input        | 3A |   |

| 54 |       | GND      | Ground                              | 1A | 1 |

| 55 | CML-O | Rx5p     | Receiver Non-Inverted Data Input    | 3A |   |

| 56 | CML-O | Rx5n     | Receiver Inverted Data Input        | 3A |   |

| 57 |       | GND      | Ground                              | 1A | 1 |

| 58 |       | GND      | Ground                              | 1A | 1 |

| 59 | CML-O | Rx6n     | Receiver Non-Inverted Data Input    | 3A |   |

| 60 | CML-O | Rx6p     | Receiver Inverted Data Input        | 3A |   |

| 61 |       | GND      | Ground                              | 1A | 1 |

| 62 | CML-O | Rx8n     | Receiver Non-Inverted Data Input    | 3A |   |

| 63 | CML-O | Rx8p     | Receiver Inverted Data Input        | 3A |   |

| 64 |       | GND      | Ground                              | 1A | 1 |

| 65 |       | NC       | No Connect                          | 3A | 3 |

| 66 |       | Reserved | For Future Use                      | 3A | 3 |

| 67 |       | VccTx1   | 3.3 V Power Supply                  | 2A | 2 |

| 68 |       | Vcc2     | 3.3 V Power Supply                  | 2A | 2 |

| 69 |       | Reserved | For Future Use                      | 3A | 3 |

| 70 |       | GND      | Ground                              | 1A | 1 |

| 71 | CML-I | Tx7p     | Transmitter Non-Inverted Data Input | 3A |   |

| 72 | CML-I | Tx7n     | TransmitterInverted Data Input      | 3A |   |

| 73 |       | GND      | Ground                              | 1A | 1 |

| 74 | CML-I | Тх5р     | Transmitter Non-Inverted Data Input | 3A |   |

| 75 | CML-I | Tx5n     | Transmitter Inverted Data Input     | 3A |   |

| 76 |       | GND      | Ground                              | 1A | 1 |

#### Notes

Note 1: QSFP-DD uues common ground (GND) for all singnals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board sgnal-common ground plane.

Note 2: VccRx, VccRx1, Vcc;, Vcc2, VccTx and VccTx1 shall be applied concurrently. Requirements defined for the host side of the Host Card Edge Connector are listed in Table 4. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination. The connector Vcc pins and each rated for a maximum current of 1000 mA.

Note 3: All Vendor Specific, Reserved and No Connect pins may be terminated with 50 ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100 pF. Note 4: Plug Sequence specifies the mating sequence of the host connector and module. The sequence specifies the mating sequence of the host connector and module, The sequence is 1A, 2A, 3A, 1B, 2B, 3B. (see Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP-DD pads. Sequence 1A, 1B will then occur simultaneously, followed by 2A, 2B followed by 3A, 3B.

# II. Absolute Maximum Ratings

Module performance is not guaranteed beyond the operating range (see Section VI). Exceeding the limits below may damage the transceiver module permanently.

| Parameter                           | Symbol            | Min     | Тур | Max        | Unit | Ref.                      |

|-------------------------------------|-------------------|---------|-----|------------|------|---------------------------|

| Maximum Supply Voltage              | Vcc               | -0.5    |     | 4.0        | V    |                           |

| Storage Temperature                 | T <sub>s</sub>    | -40     |     | +85        | °C   |                           |

| Case Operating Temperature          | T <sub>OP</sub>   | 0<br>20 |     | +70<br>*60 | °C   | c-temp<br>Limited<br>temp |

| Relative Humidity                   | RH                | 15      |     | 85         | %    | 1                         |

| Receiver Damage Threshold, per Lane | P <sub>Rdmg</sub> | 5       |     |            | dBm  |                           |

Notes:

<sup>1.</sup> Non-condensing.

# III. Electrical Characteristics (EOL, TOP = 0 to 70 °C, $V_{\rm cc}$ = 3.135 to 3.465 Volts)

| Parameter                                           | Symbol      | Min        | Тур           | Max        | Unit | Ref.                       |

|-----------------------------------------------------|-------------|------------|---------------|------------|------|----------------------------|

| Supply Voltage                                      | Vcc         | 3.135      | 3.3           | 3.465      | V    |                            |

| Supply Current                                      | Icc         |            |               | 3.83       | А    |                            |

| Module total power                                  | Р           |            |               | 12<br>10   | W    | c-temp limit-<br>ed temp 1 |

| Transmitter                                         |             |            |               |            |      |                            |

| Signaling rate per lane                             |             | 26.5625±   | 100 ppm.      |            | Gbd  |                            |

| Differential data input voltage per lane            | Vin,pp,diff | 900        |               |            | mV   | 2                          |

| Differential input return loss                      |             | Per equati | on (83E-5) II | EEE802.3bm | dB   |                            |

| Differential to common mode input re-turn loss      |             | Per equati | on (83E-6) II | EEE802.3bm | dB   |                            |

| Differential termination mismatch                   |             |            |               | 10         | %    |                            |

| Module stress input test                            |             | Per 120E.3 | 3.4.1 IEEE80  | 2.3bs      |      | 3                          |

| Single-ended voltage tolerance range                |             | -0.4       |               | 3.3        | V    |                            |

| DC common mode voltage                              |             | -350       |               | 2850       | mV   | 4                          |

| Receiver                                            |             |            |               |            |      |                            |

| Signaling rate per lane                             |             | 26.5625±   | 100 ppm.      |            | Gbd  |                            |

| AC common-mode output voltage (RMS)                 |             |            |               | 17.5       | mV   |                            |

| Differential output voltage                         |             |            |               | 900        | mV   |                            |

| Near-end ESMW (Eye symmetry mask width)             |             | 0.265      |               |            | UI   |                            |

| Near-end Eye height, differential (min)             |             | 70         |               |            | mV   |                            |

| Far-end ESMW (Eye symmetry mask width)              |             | 0.2        |               |            | UI   |                            |

| Far-end Eye height, differential (min)              |             | 30         |               |            | mV   |                            |

| Far-end pre-cursor ISI ratio                        |             | -4.5       |               | 2.5        | dB   |                            |

| Differential output return loss                     |             | Per equati | on 83E-2 IEE  | EE802.3bm  |      |                            |

| Common to differential mode con-version return loss |             | Per equati | on 83E-3 IEE  | EE802.3bm  |      |                            |

| Differential termination mismatch                   |             |            |               | 10         | %    |                            |

| Transition time (min, 20% to 80%)                   |             | 9.5        |               |            | ps   |                            |

| DC common mode voltage (min)                        |             | -350       |               | 2850       | mV   | 4                          |

#### Notes:

- $1. \, \text{Maximum total power value is specified across the full temperature and voltage range}.$

- 2. With the exception to 120E.3.1.2 that the pattern is PRBS31Q or scrambled idle.

- 3. Meets specified BER

- 4. DC common mode voltage generated by the host. Specification includes effects of ground offset voltage.

# IV. Optical Characteristics (EOL, $T_{_{\mathrm{OP}}}$ = 0 to 70 °C, $V_{_{\mathrm{CC}}}$ = 3.135 to 3.465 Volts)

| Parameter                                                          | Symbol | Min    | Тур         | Max  | Unit  | Ref. |

|--------------------------------------------------------------------|--------|--------|-------------|------|-------|------|

| Transmitter                                                        |        |        |             |      |       |      |

| Signaling rate (each lane (range)                                  |        | 53.125 | ± 100 ppm   | 1    | GBd   |      |

| Modulation format                                                  |        |        | PAM4        |      |       |      |

| Lane wavelength (range)                                            |        | 1304.  | 5 to 1317.5 |      | nm    |      |

| Side-mode suppression ratio (SMSR)                                 |        | 30     |             |      | dB    |      |

| Average launch power, each lane                                    |        |        |             | 4.5  | dBm   |      |

| Average launch power, each lane                                    |        | -2     |             |      | dBm   | 1    |

| Outer Optical Modulation Amplitude                                 |        |        |             |      |       |      |

| (OMAouter), each lane                                              |        | 1      |             | 4.7  | dBm   | 2    |

| Launch power in OMAouter minus TDECQ, each lane                    |        | -0.3   |             |      | dBm   |      |

| Transmitter and dispersion eye closure for PAM4 (TDECQ), each lane |        |        |             | 3.4  | dB    |      |

| Average launch power of OFF transmitter, each lane                 |        |        |             | -15  | dBm   |      |

| Extinction ratio                                                   |        | 3.5    |             |      | dB    |      |

| Transmitter transition time                                        |        |        |             | 17   | ps    |      |

| Transmitter over/under-shoot                                       |        |        |             | 12   | %     |      |

| RIN17.10MA                                                         |        |        |             | -136 | dB/Hz |      |

| Optical return loss tolerance                                      |        |        |             | 15.6 | dB    |      |

| Transmitter reflectance                                            |        |        |             | -26  | dB    | 3    |

### Notes:

<sup>1.</sup> Average launch power, each lane (min) is informative and not the principal indicator of signal strength. A transmitter with launch power below this value cannot be compliant; however, a value above this does not ensure compliance.

<sup>2.</sup> Even if the TDECQ < 1.4 dB for an extinction ratio of >4.5 dB or TDECQ <1.3 dB for and extinction ratio of <4.5 dB, the OMAouter (min) must exceed this value

<sup>3.</sup> Transmitter reflectance is defined looking into the transmitter

| Parameter                                           | Symbol | Min  | Тур         | Max   | Unit | Ref. |

|-----------------------------------------------------|--------|------|-------------|-------|------|------|

| Receiver                                            |        |      |             |       |      |      |

| Signaling rate (each lane (range)                   |        | 53   | 3.125 ± 100 | ppm   | GBd  |      |

| Modulation format                                   |        |      | PAM4        |       |      |      |

| Lane wavelength (range)                             |        | 1    | 304.5 to 13 | 317.5 | nm   |      |

| Damage threshold, each lane                         |        |      | 5.8         |       | dBm  | 1    |

| Average receive power, each lane                    |        |      |             | 4.8   | dBm  |      |

| Average receive power, each lane                    |        | -8.3 |             |       | dBm  | 2    |

| Receive power (OMAouter), each lane                 |        |      |             | 5     | dBm  |      |

| Receiver reflectance                                |        |      |             | -26   | dB   |      |

| Receiver sensitivity (OMAouter), each lane          |        |      |             | -6.1  | dBm  | 3    |

| Stressed receiver sensitivity (OMAouter), each lane |        |      |             | -4.1  | dBm  | 4    |

| Conditions of stressed receiver sensitivity test:   |        |      |             |       |      |      |

| Stressed eye closure for PAM4 (SECQ)                |        | 3.4  |             | dB    | 5    |      |

| SECQ - 10log <sub>10</sub> (C <sub>eq</sub> ) (max) |        |      | 3.4         |       | dBm  | 6    |

#### Notes:

- 1. The receiver shall be able to tolerate, without damage, continuous exposure to an optical input signal having this average power level.

- 2. Average receive power, each lane (min) is informative and not the principal indicator of signal strength. A received power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 3. Receiver sensitivity (OMAouter), each lane (max) is informative and is defined for a transmitter with SECQ of 3.4 dB. Receiver sensitivity (OMA outer) (max) for 100GBASE-LR1 is defined for a transmitter with a value of SECQ up to 1.4 dB and for values of SECQ greater than 1.4 dB see equation (140-2) and equation (140-3) respectively)

- 4. Measured with conformance test signal at TP3 (see 124.8.9) for the BER specified in 124.1.1.

- 5. These test conditions are for measuring stressed receiver sensitivity. They are not characteristics of the receiver.

- 6. C<sub>en</sub> is a coefficient defined in 121.8.5.3, which accounts for these reference equalizer noise enhancement.

# V. General Specifications

| Parameter                           | Symbol |  | Тур | Max    | Units | Ref. |

|-------------------------------------|--------|--|-----|--------|-------|------|

| Bit Rate (all wavelengths combined) | BR     |  |     | 425    | Gb/s  |      |

| Bit Error Ratio                     | BER    |  |     | 2.4E-4 |       | 1    |

| Maximum Supported Distances         |        |  |     |        |       |      |

| Fiber Type                          |        |  |     |        |       |      |

| SMF per G.652                       | Lmax1  |  |     | 10,000 | m     |      |

#### Notes:

1. As defined by IEEE P802.3bs.

### VI. Environmental Specifications

Finisar FTCD4543E2PxM 4x100G-LR QSFP-DD transceivers have an operating case temperature range of 0°C to +70°C.

| Environmental Specifications | Symbol           | Min | Тур | Max | Units | Ref. |

|------------------------------|------------------|-----|-----|-----|-------|------|

| Case Operating Temperature   | T <sub>op</sub>  | 0   |     | 70  | °C    |      |

| Storage Temperature          | T <sub>sto</sub> | -40 |     | 85  | °C    |      |

## VII. Regulatory Compliance

Finisar FTCD4543E2PxM 4x100G-LR QSFP-DD transceivers are Class 1 Laser Products. They are certified per the following standards:

| Feature          | Agency   | Standard                                    |

|------------------|----------|---------------------------------------------|

| Laser Eye Safety | FDA/CDRH | CDRH 21 CFR 1040 and Laser Notice 50        |

|                  | TÜV      | EN 60825-1: 2007<br>IEC 60825-2: 2004+A1+A2 |

|                  | TÜV      | EN 60950                                    |

|                  | UL/CSA   | CLASS 3862.07<br>CLASS 3862.87              |

Copies of the referenced certificates are available at Finisar Corporation upon request.

#### **VIII. Digital Diagnostics Functions**

FTCD4543E2PxM 4x100G-LR QSFP-DD transceivers support the I2C-based diagnostics interface specified by the SFF Commitee<sup>1</sup>. See also Finisar Application Note AN-20xx (TBD).

#### **IX. Memory Contents**

Per QSFP-DD MSA Specification1. See Finisar Application Note AN-20xx (TBD).

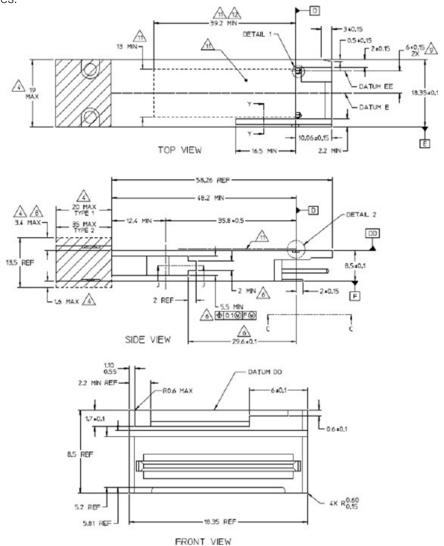

# **XI. Mechanical Specifications**

Finisar FTCD4543E2PxM 4x100G-LR QSFP-DD transceivers are compatible with the QSFP-DD Type 2 Specification for pluggable form factor modules.

Figure 2. FTCD4543E2PxM Mechanical Dimensions.

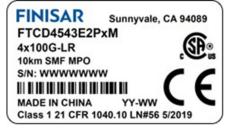

Figure 3. Product Label

#### XII. References

- 1. QSFP-DD Specification for QSFP Double Density 8X Pluggable Transceiver

- 2. IEEE P802.3cu: 100Gb/s and 400Gb/s Operation over Single-Mode Fibre at 100Gb/s per Wavelength

- 3. SFF-8665: "QSFP+ 28Gb/s 4X Pluggable Transceiver Solution (QSFP28)", Rev 1.9, June 29, 2015 and associated SFF documents referenced therein:

i. SFF-8661

ii. SFF-8679

iii. SFF-8636

iv. SFF-8662

v. SFF-8663

vi. SFF-8672

vii. SFF-8683

- 4. Directive 2011/65/EU of the European Council Parliament and of the Council, "on the restriction of the use of certain hazardous substances in electrical and electronic equipment" as well as Commission Delegated Directive (EU) 2015/863 amending Annex II to Directive 2011/65/EU. Certain products may use one or more exemptions as allowed by the Directive. 5. "Application Note AN-2038: Finisar Implementation Of RoHS Compliant Transceivers", Finisar Corporation, January 21, 2005.

- 6. Application Note AN-2153, Initialization, Finisar Corporation.

- 7. Application Note AN-2154, EEPROM Map, Finisar Corporation.

- 8. IEEE P802.3bs, 400GAUI-8 Interface.